Acerca de este curso

- Orientation

- In this module you will become familiar with the course and our learning environment. The orientation will also help you obtain the technical skills required for the course.

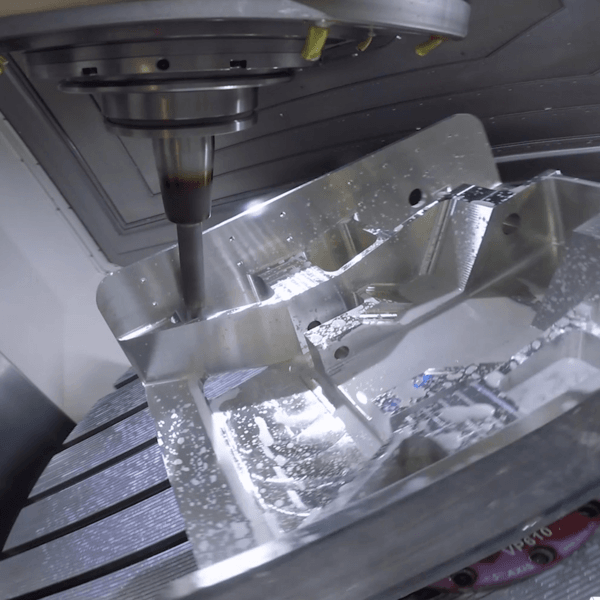

- ASIC Placement

- In this second part of our course, we will talk about geometry. We will begin with an overview of the ASIC layout process, and discuss the role of technology libraries, tech mapping (a topic we delay until the following week, to let those who want to do the Placer programming assignment have more time), and placement and routing. In this set of lectures, we focus on the placement process itself: you have a million gates from the result of synthesis and map, so, where do they go? This process is called “placement”, and we describe an iterative method, and a mathematical optimization method, that can each do very large placement tasks.

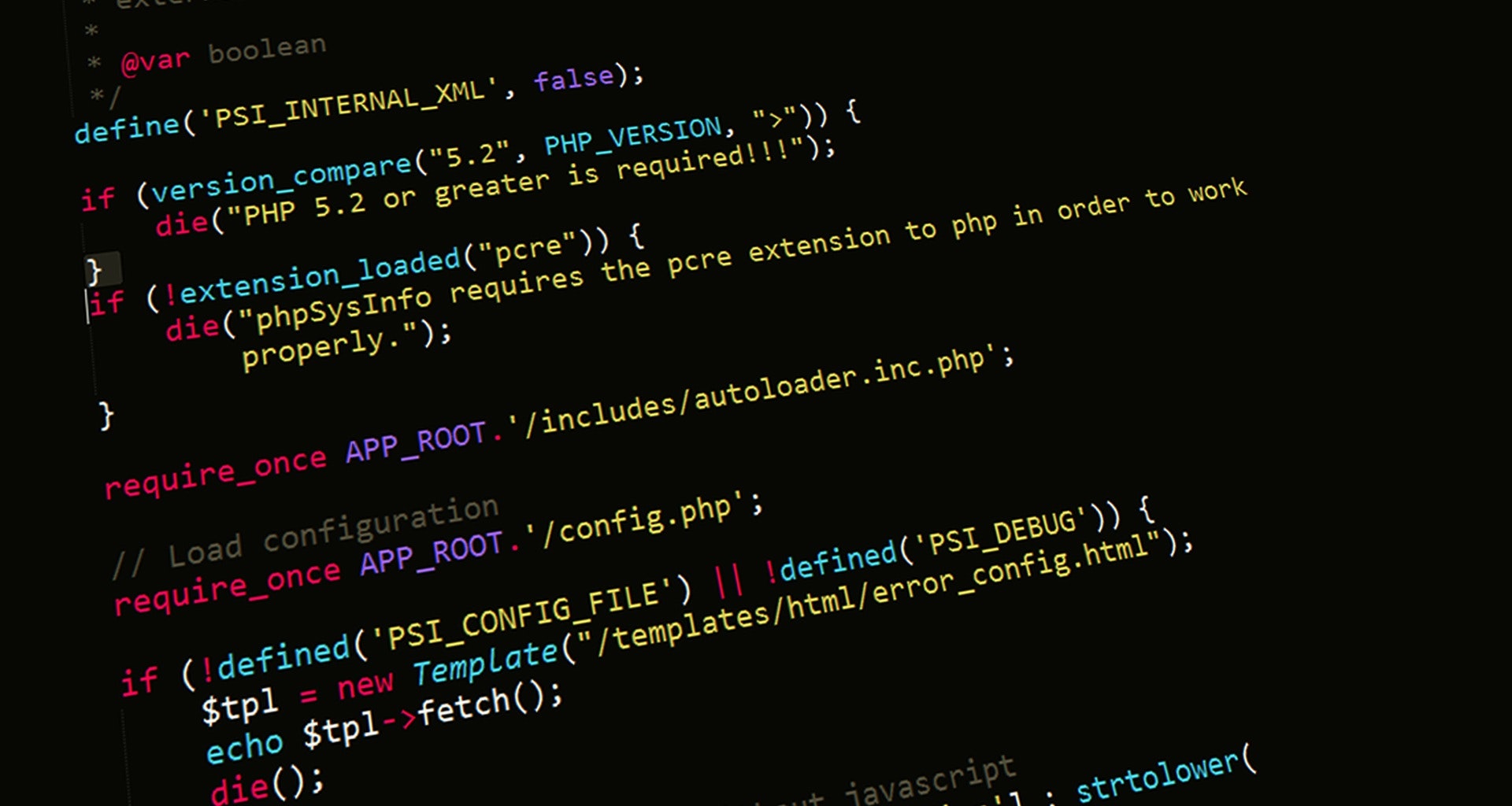

- Technology Mapping

- Technology Mapping! We omitted one critical step between logic and layout, the process of translating the output of synthesis -- which is NOT real gates in your technology library -- into real logic gates. The Tech Mapper performs this important step, and it is a surprisingly elegant algorithm involving recursive covering of a tree. Another place where knowing some practical computer science comes to the rescue in VLSI CAD.

- ASIC Routing

- Routing! You put a few million gates on the surface of the chip in some sensible way. What's next? Create the wires to connect them. We focus on Maze Routing, which is a classical and powerful technique with the virtue that one can "add" much sophisticated functionality on top of a rather simple core algorithm. This is also the topic for final (optional) programming assignment. Yes, if you choose, you get to route pieces of the industrial benchmarks we had you place in the placer software assignment.

- Timing Analysis

- You synthesized it. You mapped it. You placed it. You routed it. Now what? HOW FAST DOES IT GO? Oh, we need some new models, to talk about how TIMING works. Delay through logic gates and big networks of gates. New numbers to understand: ATs, RATs, SLACKS, etc. And some electrical details (minimal) to figure out how delays happen through the physical geometry of physical routed wires. All together this is the stuff of Static Timing Analysis (STA), which is a huge and important final "sign off" step in real ASIC design.

- Final Exam

- There is no new content this week. Instead, you should focus on finishing the last problem set and completing the Final Exam.

Cursos relacionados

GRATIS Aprendiendo a aprender: Poderosas herramientas mentales…

Deep teaching solutions

Español

GRATIS Programación para todos (Introducción a Python)

University of Michigan

Inglés

GRATIS The Science of Well-Being

Yale

Inglés

GRATIS Negociación exitosa: Estrategias y habilidades esenciales

University of Michigan

Inglés

GRATIS Primeros Auxilios Psicológicos (PAP)

Universitat Autónoma de Barcelona

Español